Processo A16, tecnologia NanoFlex, riduzione dei costi per il nodo a 4nm, soluzione System-on-Wafer, integrazione della fotonica del silicio e packaging avanzato per il settore automobilistico: sono queste le novità annunciata durante la 30^ edizione del TSMC North America Technology Symposium 2024.

Processo A16, tecnologia NanoFlex, riduzione dei costi per il nodo a 4nm, soluzione System-on-Wafer, integrazione della fotonica del silicio e packaging avanzato per il settore automobilistico: sono queste le novità annunciata durante la 30^ edizione del TSMC North America Technology Symposium 2024.

Anche quest’anno, TSMC ha scelto il suo North America Technology Symposium di Santa Clara, in California, per offrire un aggiornamento sulle tecnologie che l’azienda – prima foundry al mondo – metterà a disposizione dei propri clienti per i loro progetti più avanzati di semiconduttori.

All’evento hanno partecipato quest’anno più di 2.000 persone, rispetto alle 100 persone di 30 anni fa. Il North America Technology Symposium darà il via ai simposi tecnologici di TSMC in tutto il mondo nei prossimi mesi.

“Stiamo entrando in un mondo basato sull’intelligenza artificiale, in cui l’intelligenza artificiale non funziona solo nei data center, ma anche nei PC, nei dispositivi mobili, nelle automobili e persino nell’Internet delle cose”, ha affermato CC Wei, CEO di TSMC. “Noi di TSMC offriamo ai nostri clienti l’insieme più completo di tecnologie per realizzare le loro visioni sull’intelligenza artificiale, dal silicio più avanzato al mondo, al più ampio portafoglio di packaging avanzati e piattaforme IC 3D, alle tecnologie speciali che integrano il mondo digitale con il mondo reale.”

Tra le novità, la tecnologia TSMC A16 (nessuna relazione con A16 Bionic) caratterizzata da transistor nanosheet con un’innovativa soluzione di power rail sul retro che sarà in produzione nel 2026, con densità e prestazioni notevolmente migliorate e la tecnologia System-on-Wafer (TSMC-SoW), una soluzione innovativa per portare prestazioni rivoluzionarie a livello wafer nell’affrontare i futuri requisiti di intelligenza artificiale per i data center hyperscaler.

Ma procediamo con ordine.

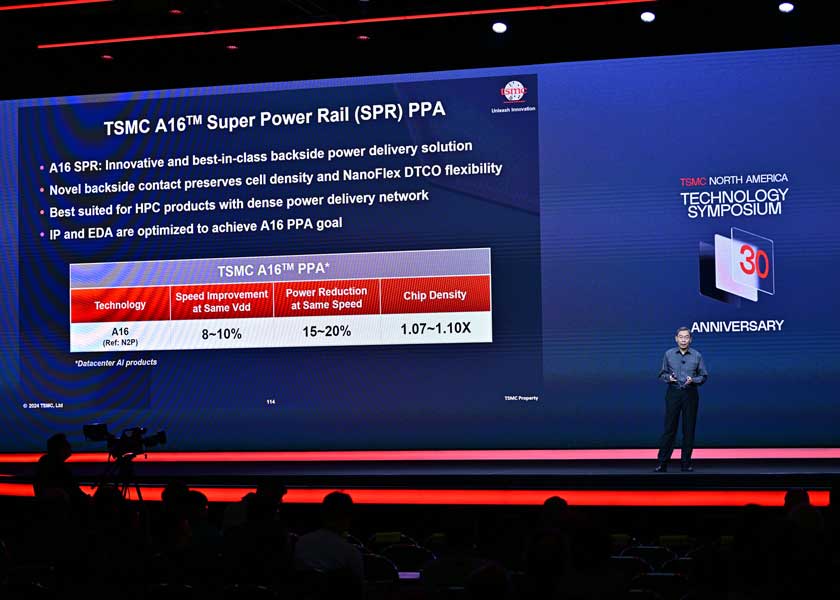

Tecnologia TSMC A16

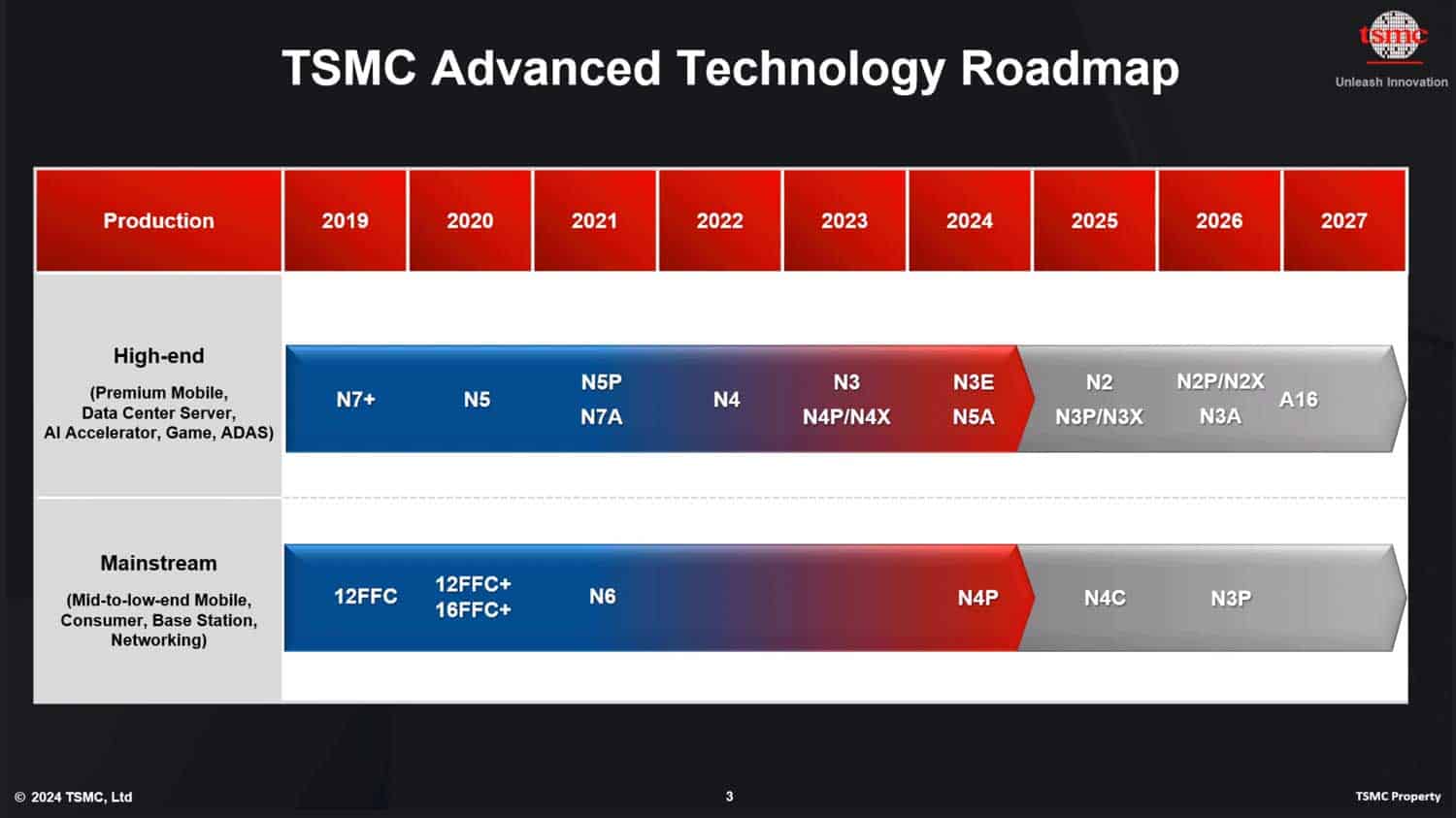

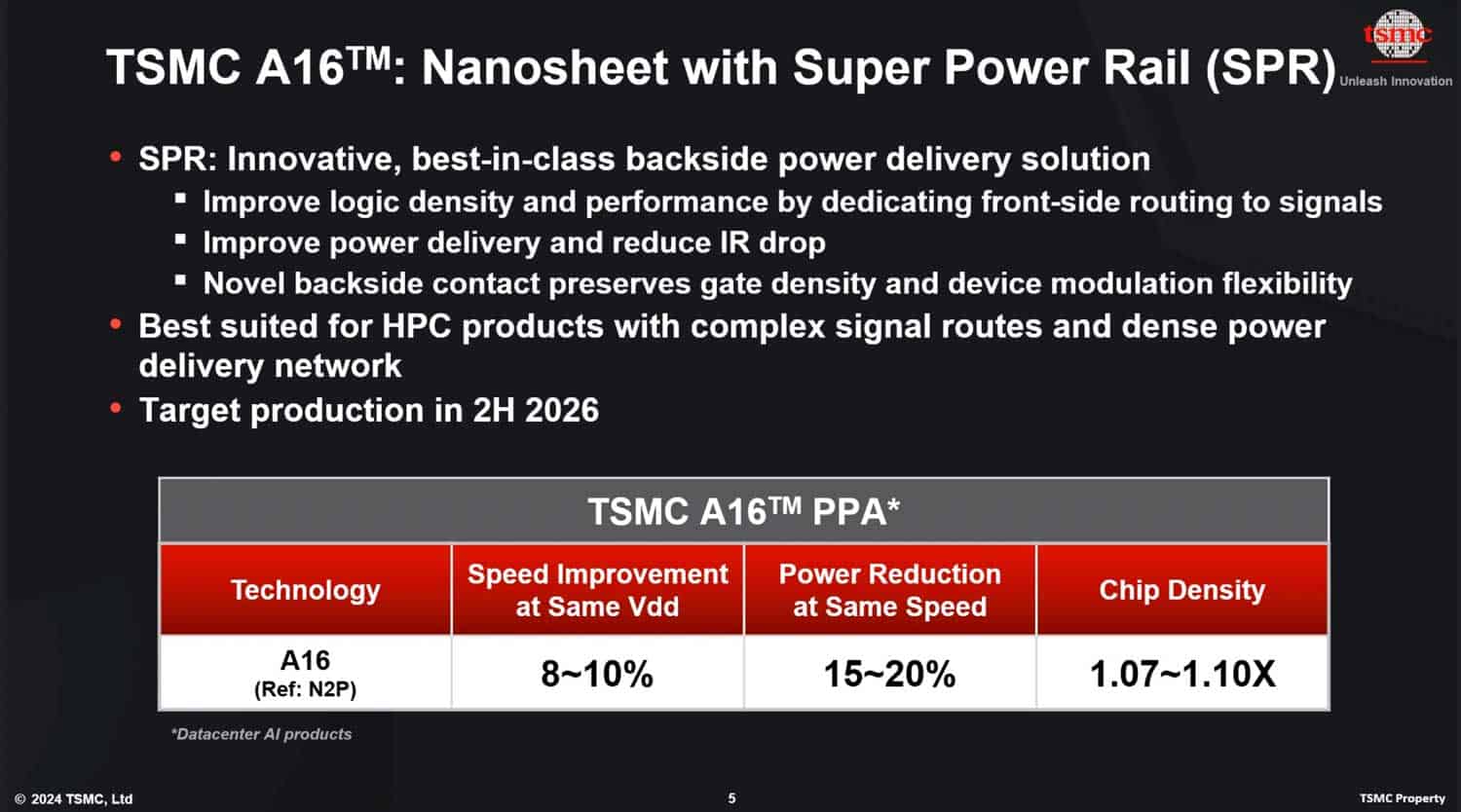

Con la tecnologia N3E attualmente in produzione e N2 sulla buona strada per entrare in produzione nella seconda metà del 2025, TSMC ha presentato A16, la prossima tecnologia della sua roadmap a 1,6 nm, la prima di “classe angstrom”. A16 combinerà l’architettura Super Power Rail di TSMC con i transistor gate-all-around (GAAFET) e verrà utilizzata per la produzione in volumi nel 2026.

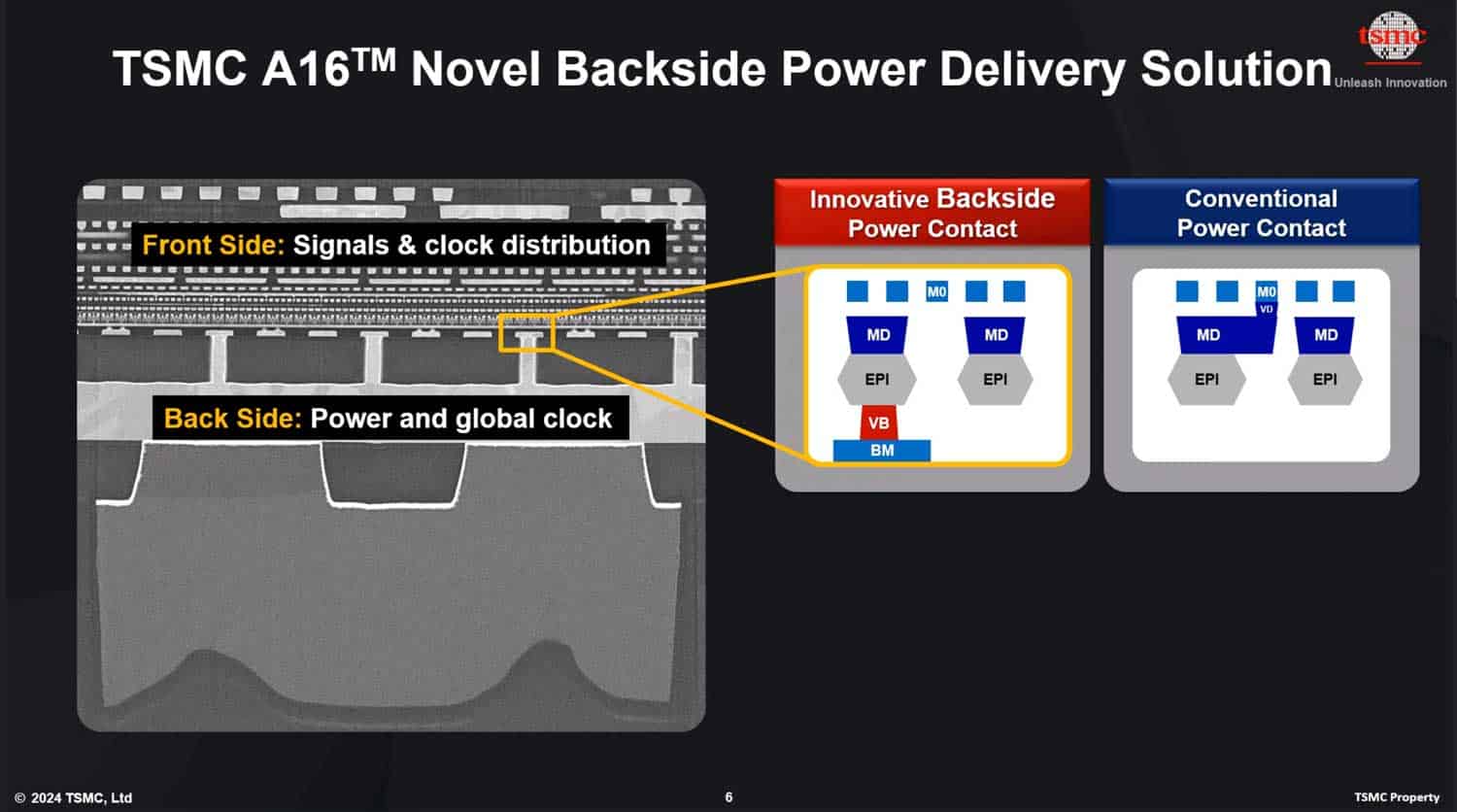

Secondo TSMC questa soluzione migliora la densità logica e le prestazioni dedicando risorse di routing front-side ai segnali, rendendo A16 ideale per prodotti HPC con percorsi di segnale complessi e fitte reti di erogazione di energia. Rispetto al processo N2P di TSMC, A16 fornirà un miglioramento della velocità dell’8-10% a parità di tensione di alimentazione, una riduzione della potenza del 15-20% alla stessa velocità e un miglioramento della densità del chip fino a 1,10X per i prodotti per data center.

La novità di questo nodo è la rete di distribuzione dell’alimentazione Super Power Rail (SPR) posta sul retro del dispositivo, una novità assoluta per TSMC. Più che la riduzione delle dimensioni del design, questa tecnologia, che doveva essere inizialmente introdotta col nodo N2P, rappresenta il vero spartiacque con le generazioni precedenti di processi di TSMC.

Rispetto alle tecnologie BSPDN concorrenti (Buried Power Rail di Imec e PowerVia di Intel), Super Power Rail è probabilmente la più efficiente in termini di ridimensionamento dell’area, ma è la più complessa in fase di produzione.

Il fatto che questa tecnologia non sia stata utilizzata per N2P suggerisce che TSMC abbia preferito una soluzione più economica e meno complessa, nonché più veloce da implementare, per l’ultimo nodo della famiglia pre-angstrom.

Considerate le tempistiche, il nodo produttivo A16 competerà presumibilmente con il nodo 14A di Intel ma a differenza di quest’ultimo che verrà prodotto con gli avanzati impianti litografici EUV High-NA di ASML, TSMC utilizzerà le tradizionali e più economiche macchine EUV sfruttando sistemi avanzati di modellazione del pattern come Centura Sculpta di Applied Materials per ridurre a non più di due il numero di passaggi.

Vale la pena ricordare che è stato proprio la scelta di Intel (principalmente per ragioni economiche) di non adottare subito la tecnologia EUV per il processo a 10 nm che ha consentito a TSMC e Samsung di avvantaggiarsi sull’azienda californiana.

Sembra ora che i ruoli si siano invertiti, con Intel che ha adottato, non appena disponibile, la tecnologia EUV High-NA mentre i rivali asiatici sono rimasti fedeli alla tecnologia EUV più tradizionale.

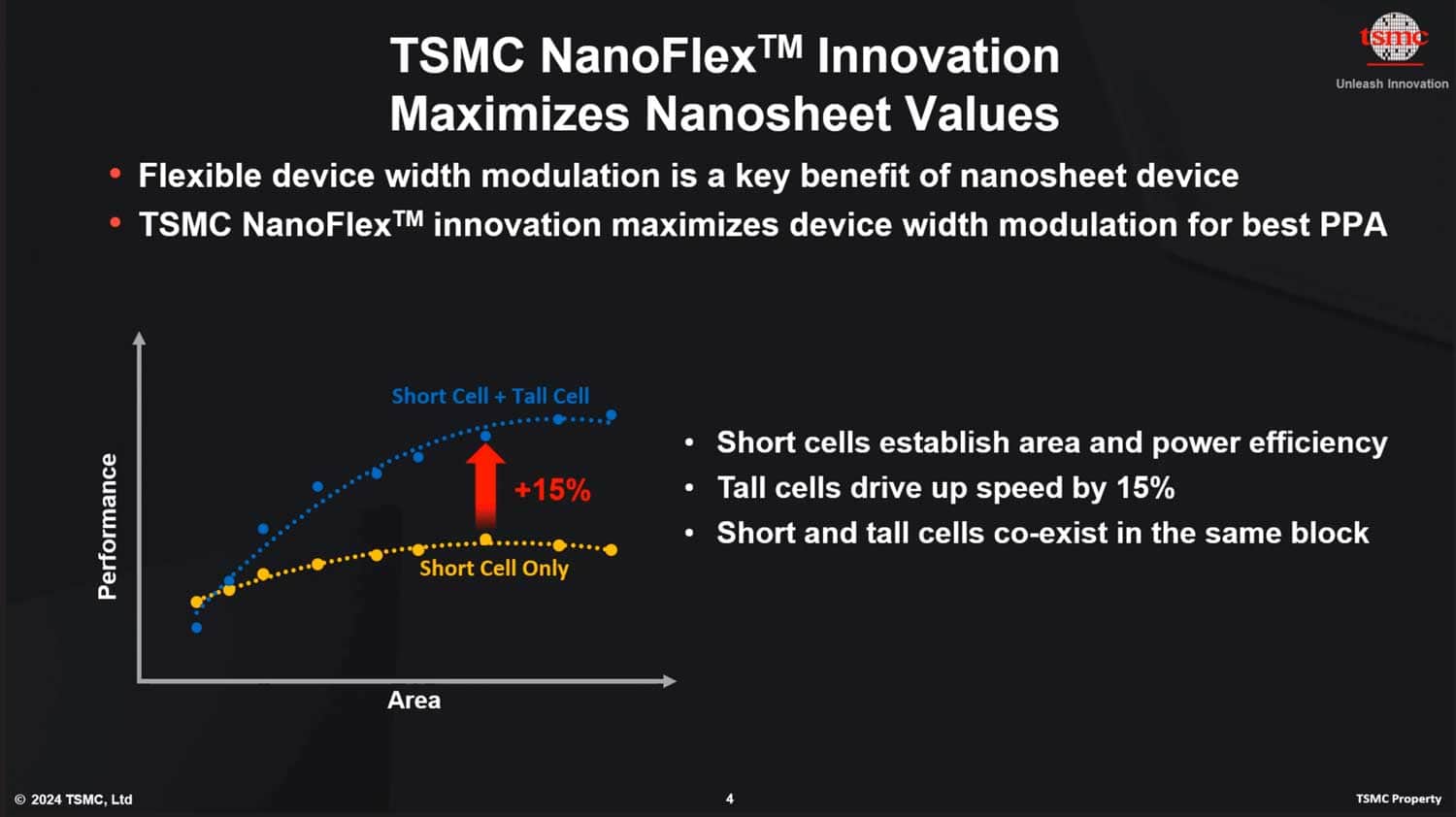

Tecnologia NanoFlex per transistor Nanosheet

L’altro annuncio riguarda la tecnologia NanoFlex per l’ottimizzazione della tecnologia di progettazione del processo N2. TSMC NanoFlex offre ai progettisti maggiore flessibilità nelle celle standard N2, consentendo di utilizzare celle provenienti da librerie diverse sullo stesso wafer. Di solito, un progettista deve utilizzare gli stessi blocchi sul chip scegliendo tra librerie “a basso consumo”, “ad alta densità” o “ad alte prestazioni”, a seconda delle caratteristiche più importanti che il chip deve garantire.

Consentendo ai progetti di utilizzare blocchi provenienti da librerie diverse, è possibile raggiungere il compromesso ottimale in termini di potenza, prestazioni e area.

Tecnologia N4C

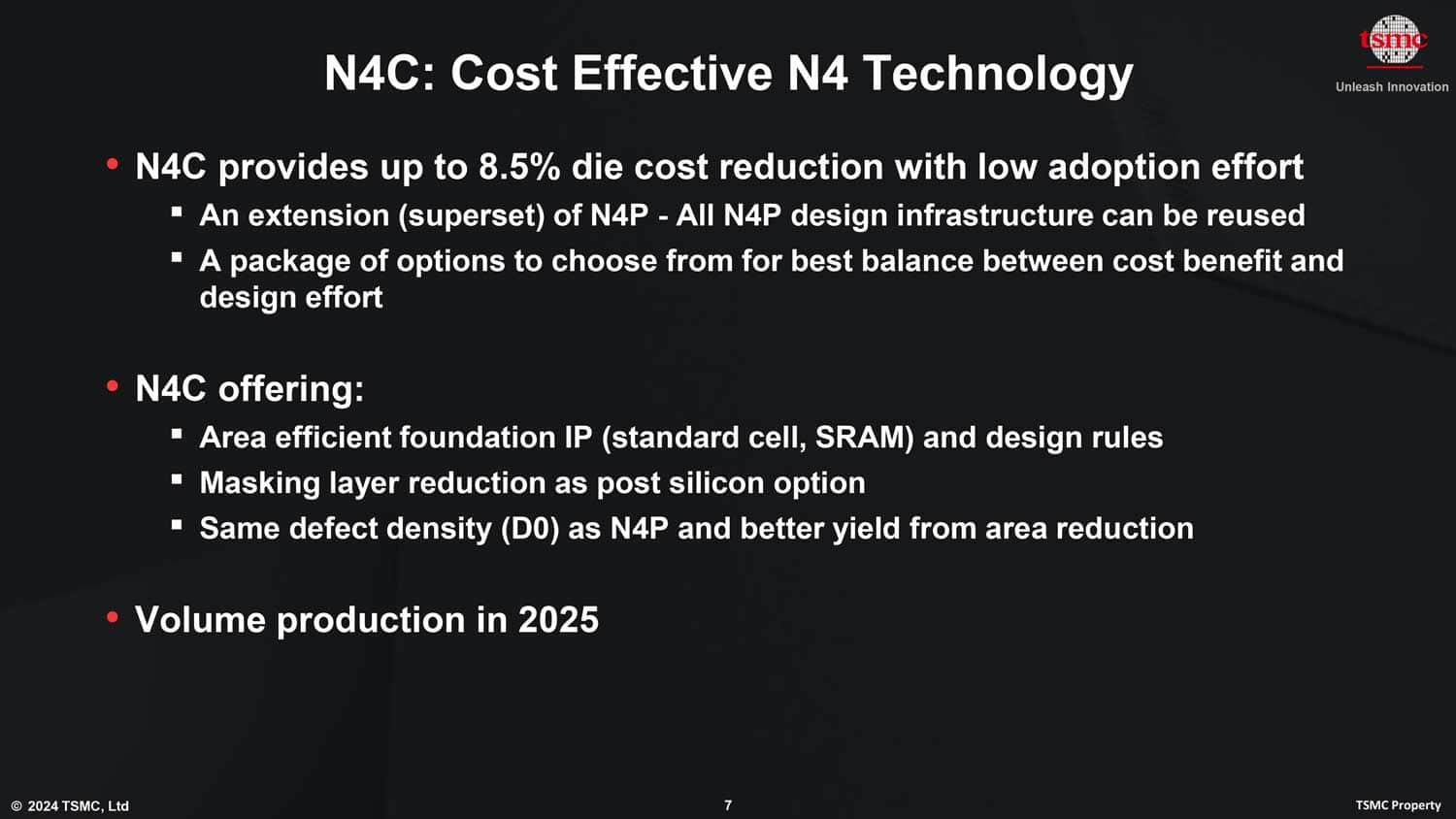

Per portare la tecnologia avanzata di TSMC a una gamma più ampia di applicazioni, l’azienda ha annunciato N4C, un’estensione della tecnologia N4P con una riduzione del costo del die fino all’8,5% e un basso sforzo di adozione. La produzione in volumi è prevista per il 2025.

Per i clienti che per ragioni di costo non potranno adottare il processo N3E, N4C offre un’opzione economicamente vantaggiosa per la migrazione verso le tecnologie più avanzate. I miglioramenti riguardano la riprogettazione della cella standard e della cella SRAM, la modifica di alcune regole di progettazione e la riduzione del numero di strati di mascheratura.

Le minori dimensioni del die, a parità di densità, miglioreranno il rendimento nonché la complessità della produzione.

CoWoS, SoIC e System-on-Wafer (TSMC-SoW)

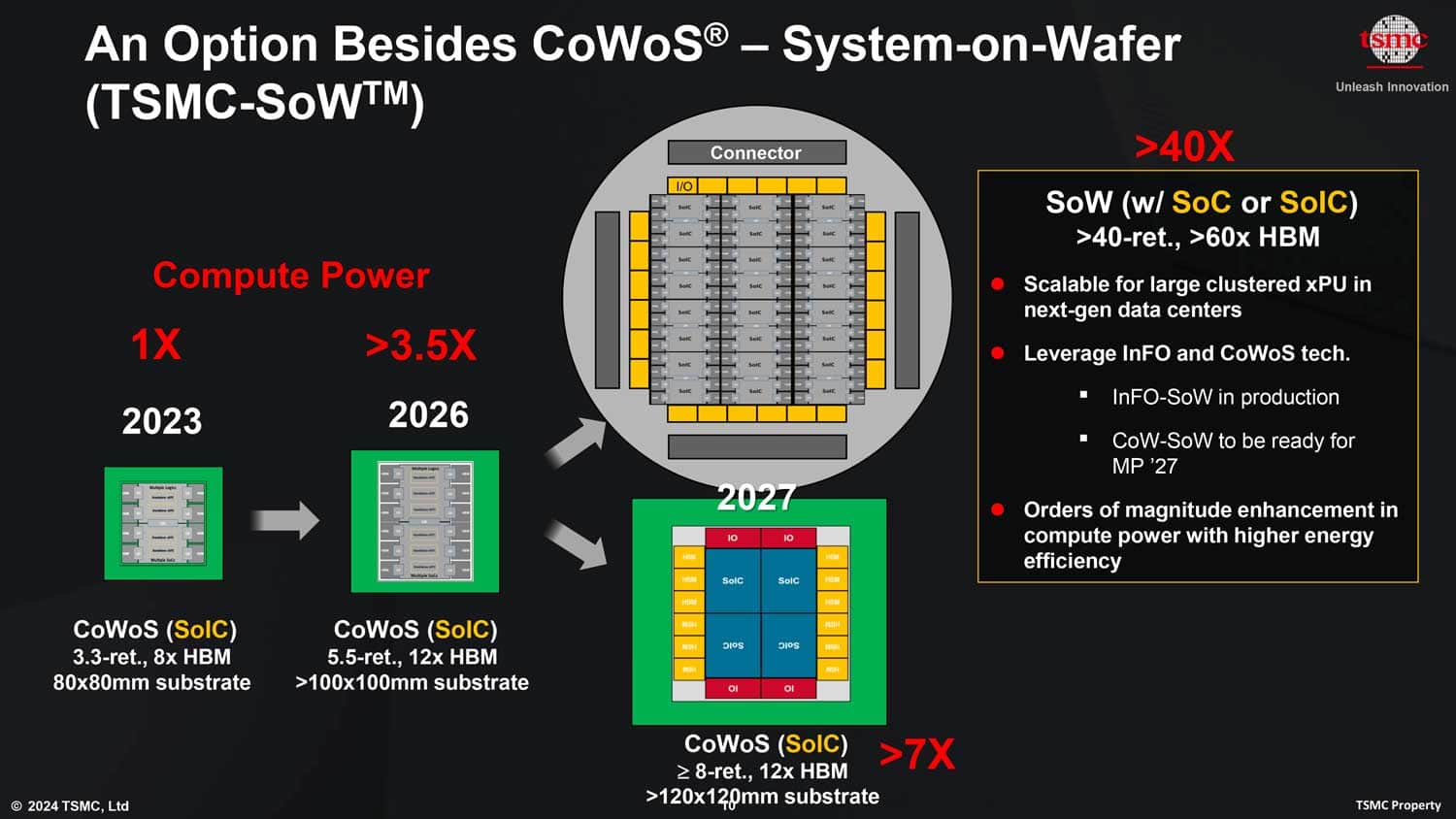

La tecnologia Chip on Wafer on Substrate (CoWoS) di TSMC è stato un fattore chiave per la rivoluzione dell’intelligenza artificiale consentendo di collegare GPU/xPU, un chip logico e HBM su un substrato chiamato interposer. Si tratta di una tecnologia di packaging 2.5D poiché il chip logico e l’HBM impilato verticalmente (3D) sono integrati in un modulo posizionato su un substrato del package orizzontale (2D) consentendo di includere più core del processore e memoria a larghezza di banda elevata (HBM).

Allo stesso tempo, il System on Integrated Chips (SoIC) si è affermato come la soluzione leader per lo stacking di chip 3D, con i clienti che abbinano sempre più CoWoS a SoIC e altri componenti per la massima integrazione system-in-package (SiP).

Con la sua piattaforma system-on-wafer di prossima generazione, TSMC prevede di riunire due delle sue tecnologie di packaging: InFO-SoW e System on Integrated Chips (SoIC) per impilare memoria o logica su un system-on-wafer utilizzando il metodo Chip-on-Wafer (CoW). La tecnologia CoW-SoW sarà pronta per la produzione di massa nel 2027.

Con System-on-Wafer, TSMC offre una nuova opzione rivoluzionaria per abilitare un’ampia gamma di die su un wafer da 300 mm, offrendo maggiore potenza di elaborazione e occupando molto meno spazio, con un aumento di prestazioni per watt di molti ordini di grandezza. La prima offerta SoW di TSMC, un wafer di sola logica basato sulla tecnologia Integrated Fan-Out (InFO), è già in produzione.

Nel 2027 è prevista la disponibilità di una versione chip-on-wafer che sfrutta la tecnologia CoWoS, consentendo l’integrazione di SoIC, HBM e altri componenti per creare un potente sistema a livello wafer con una potenza di calcolo paragonabile a un rack di server di un data center o addirittura a un intero server.

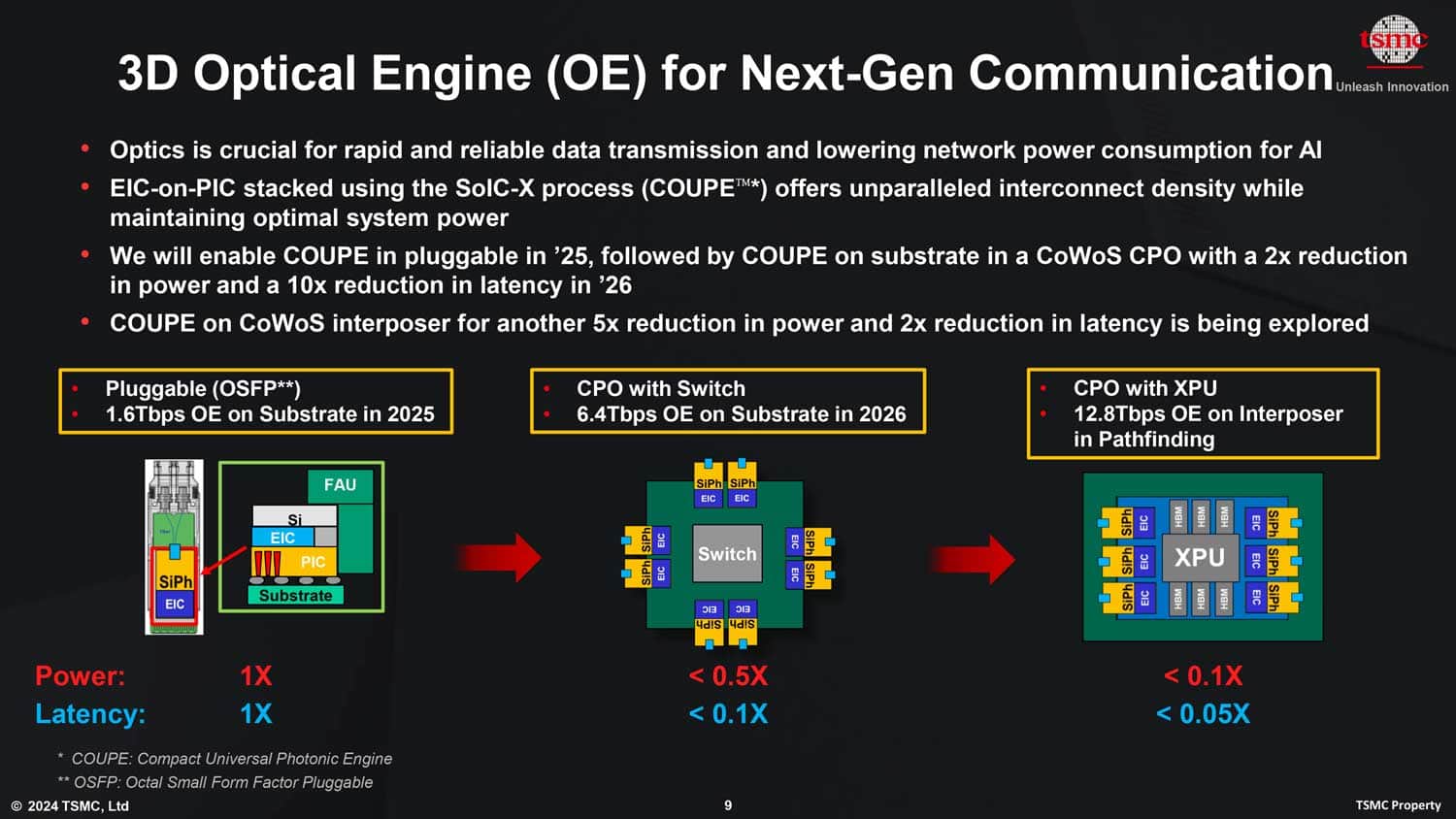

Integrazione della fotonica del silicio

TSMC sta sviluppando la tecnologia COUPE (Compact Universal Photonic Engine) per supportare la crescita esponenziale della trasmissione dei dati che accompagna il boom dell’intelligenza artificiale. COUPE utilizza la tecnologia di impilamento dei chip SoIC-X per impilare un die elettrico sopra un die fotonico, offrendo l’impedenza più bassa sull’interfaccia die-to-die e una maggiore efficienza energetica rispetto ai metodi di impilamento convenzionali. TSMC prevede di qualificare COUPE per i pluggable con fattore di forma ridotto nel 2025, seguita dall’integrazione nel packaging CoWoS come ottica co-confezionata (CPO) nel 2026, portando le connessioni ottiche direttamente nel package.

Il motore ottico 3D di prima generazione offrirà una velocità di trasferimento di 1,6 Tbps; la versione successiva, progettata per integrarsi nel packaging CoWoS come ottica co-confezionata con uno switch, supporterà una velocità di trasferimento fino a 6,40 Tbps mentre l’ultima versione migliorerà ulteriormente la velocità sino a 12,8 Tbps.

Packaging avanzato per il settore automobilistico

Dopo aver introdotto il processo N3AE “Auto Early” nel 2023, TSMC continua a soddisfare le esigenze dei clienti automobilistici per una maggiore potenza di calcolo che soddisfi le esigenze di sicurezza e qualità dell’automotive integrando silicio avanzato con packaging avanzato. TSMC sta sviluppando soluzioni InFO-oS e CoWoS-R per applicazioni quali sistemi avanzati di assistenza alla guida (ADAS), controllo del veicolo e computer centrali del veicolo, con l’obiettivo di qualificarsi AEC-Q100 Grado 2 entro il quarto trimestre del 2025.