SK hynix adotterà il processo di fonderia all’avanguardia di TSMC per migliorare le prestazioni dell’HBM4.

SK hynix ha annunciato di aver firmato un memorandum d’intesa con TSMC per produrre HBM (High Bandwidth Memory) di prossima generazione e migliorare la logica e l’integrazione HBM attraverso una tecnologia di packaging avanzata. Attraverso questa iniziativa, l’azienda prevede di procedere con lo sviluppo di prodotti HBM4, ovvero la sesta generazione della famiglia HBM, la cui produzione in serie è prevista a partire dal 2026.

SK hynix ha affermato che la collaborazione tra il leader globale nel settore delle memorie AI e TSMC, una delle principali fonderie logiche a livello mondiale, porterà a ulteriori innovazioni nella tecnologia HBM. Si prevede inoltre che la collaborazione consenta innovazioni nelle prestazioni della memoria attraverso la collaborazione trilaterale tra progettazione del prodotto, fonderia e fornitore di memoria.

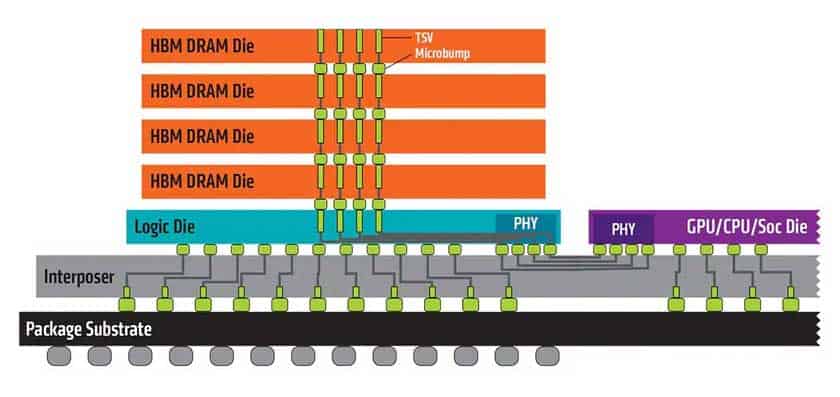

Le due società si concentreranno innanzitutto sul miglioramento delle prestazioni del die di base utilizzato nella parte inferiore del package HBM. L’HBM è realizzato impilando un die core DRAM sopra un die base che utilizza la tecnologia TSV (Through Silicon Via) per collegare verticalmente il chip logico di base a un certo numero di strati DRAM. Possono esserci migliaia di TSV pass-through a seconda del design del chip. Il die di base situato nella parte inferiore è collegato alla GPU che controlla l’HBM.

SK hynix ha utilizzato una tecnologia proprietaria per realizzare matrici base fino a HBM3E, ma prevede di adottare il processo logico avanzato di TSMC per la matrice base HBM4 per aggiungere funzionalità aggiuntive in uno spazio limitato. Ciò aiuterà anche SK hynix a produrre HBM personalizzati per soddisfare specifiche richieste di clienti in termini di prestazioni ed efficienza energetica.

SK hynix e TSMC hanno inoltre deciso di collaborare per ottimizzare l’integrazione della tecnologia HBM di SK hynix e CoWoS (Chip on Wafer on Substrate) di TSMC, collaborando al tempo stesso per rispondere alle richieste comuni dei clienti relative alla HBM.

CoWoS è un processo di packaging proprietario di TSMC che collega GPU/xPU, un chip logico e HBM, su un substrato speciale chiamato interposer. Viene anche chiamato packaging 2.5D poiché il chip logico e l’HBM impilato verticalmente (3D) sono integrati in un modulo posizionato su un substrato del package orizzontale (2D)

I commenti

“Ci aspettiamo una forte partnership con TSMC per contribuire ad accelerare i nostri sforzi in una collaborazione aperta con i nostri clienti per sviluppare l’HBM4 più performante del settore”, ha affermato Justin Kim, presidente e responsabile di AI Infra, presso SK hynix. “Con questa cooperazione rafforzeremo ulteriormente la nostra leadership di mercato come fornitore totale di memorie AI aumentando la competitività nello spazio della piattaforma di memoria personalizzata”.

“TSMC e SK hynix hanno già stabilito una forte partnership nel corso degli anni. Abbiamo lavorato insieme per integrare la logica più avanzata e l’HBM all’avanguardia per fornire le soluzioni di intelligenza artificiale leader a livello mondiale”, ha affermato il dott. Kevin Zhang, Senior Vice President of TSMC’s Business Development and Overseas Operations Office, and Deputy Co-Chief Operating Officer. “Guardando avanti alla prossima generazione di HBM4, siamo fiduciosi che continueremo a lavorare a stretto contatto per fornire le migliori soluzioni integrate per sbloccare nuove innovazioni AI per i nostri clienti comuni.”