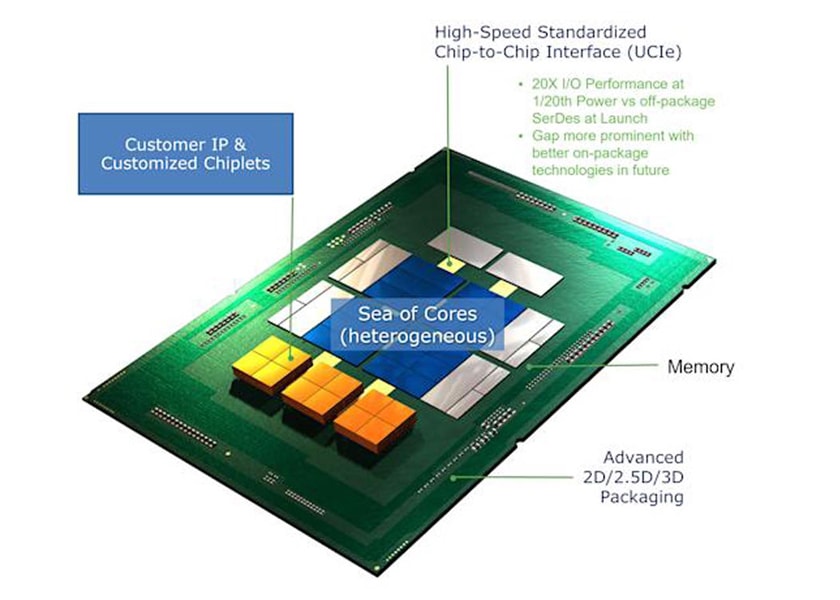

Il nuovo consorzio, denominato Universal Chiplet Interconnect Express (UCIe), ha lo scopo di definire uno standard globale di interconnessione per i “chiplet”, la nuova frontiera per mantenere in vita la legge di Moore.

Intel, TSMC e Samsung lavoreranno insieme per stabilire uno standard industriale per le tecnologie avanzate di packaging dei chip, il prossimo campo di battaglia nella corsa per costruire microchip sempre più potenti.

I tre maggiori produttori di chip del mondo, insieme a diverse altre aziende, hanno annunciato ieri che daranno vita ad un consorzio pensato per facilitare le connessioni “die-to-die”; in questo modo sarà possibile combinare componenti di diverse aziende per realizzare dispositivi sempre più performanti.

L’alleanza ha già ratificato una specifica UCIe 1.0.

Si tratta della più importante collaborazione di sempre nel settore dei semiconduttori. Oltre alle aziende già citate, al consorzio aderiscono, tra gli altri, AMD, Qualcomm, Arm, Google Cloud, Meta, Microsoft, e ASE Technology Holding, il più grande fornitore mondiale di servizi di packaging e test.

Col raggiungimento dei limiti fisici nei processi di lavorazione del silicio, queste tecnologie, un tempo considerate marginali nella produzione di microchip, emergono come un importante campo di battaglia per i principali produttori, in modo particolare per TSMC, Samsung e Intel.

Lo sviluppo dei semiconduttori fino ad ora si è concentrato principalmente su come implementare più transistor sulla base di silicio: in generale, più transistor si traducono in una maggiore potenza di calcolo. Ma poiché lo spazio tra i transistor si è ridotto a pochi nanometri, questo approccio è diventato più impegnativo, portando alcuni a prevedere la fine della legge di Moore. Pertanto le tecnologie che consentono di impilare e combinare più pezzetti di silicio sono diventate determinanti per migliorare le prestazioni dei futuri processori.

Il nuovo consorzio, denominato Universal Chiplet Interconnect Express (UCIe), mira a stabilire standard comuni per il packaging dei singoli chip, favorendo la collaborazione tra i vari produttori

Google e AMD, entrambi membri del consorzio, sono stati tra i primi ad adottare le avanzate tecnologie di stacking 3D di TSMC.

Apple, che non è entrata a far parte del consorzio, è stata la prima a utilizzare le tecnologie di stacking dei chip di TSMC sviluppate internamente nel 2016 e ha continuato a utilizzare tali tecnologie nei suoi ultimi processori per iPhone.

Anche il colosso cinese Huawei Technologies, che non fa ancora parte del consorzio, sta spingendo al massimo per sviluppare internamente tecnologie di stacking e packaging per i suoi chip, in risposta anche all’impossibilità di avanzare nelle tecnologie di front-end a causa delle sanzioni imposte dagli Stati Uniti.

UCIe intende definire uno standard di interconnessione “die-to-die” completo che renderà facile per gli utenti finali mescolare e abbinare i componenti del chiplet. Ciò significa che saranno in grado di creare system-on-a-chip (SoC) personalizzati utilizzando parti di diversi fornitori.