Il nuovo sistema di modellatura Centura Sculpta offre un’alternativa più semplice, rapida ed economica alla doppia modellatura EUV riducendo anche l’impatto ambientale. Applied Materials presenta anche il nuovo sistema di metrologia eBeam che apre la strada alla litografia EUV ad alto NA.

Mentre tutta l’attenzione mediatica era rivolta alle decisioni di ASML e Tokyo Electron riguardanti l’embargo nei confronti della Cina di sistemi avanzati per la produzione di semiconduttori, la notizia diffusa dal produttore statunitense Applied Materials relativa ad una importante svolta tecnologica riguardante la possibilità di creare transistor ad alte prestazioni e cablaggi di interconnessione con meno passaggi di litografia EUV, riducendo così il costo, è passata quasi inosservata.

Eppure si tratta, insieme al nuovo sistema di metrologia denominato eBeam, di una tecnologia che può ritardare ulteriormente lo sforzo della Cina di raggiungere una produzione di semiconduttori all’avanguardia.

Annunciato il 28 febbraio, Centura Sculpta dovrebbe consentire di ridurre il numero di passaggi litografici EUV (ultravioletti estremi) utilizzati per fabbricare circuiti integrati nei nodi di processo più avanzati, riducendo significativamente sia la complessità che i costi.

Le sanzioni statunitensi vietano già l’esportazione di strumenti litografici EUV verso la Cina. Senza di essi, i processi a 7 nm e 5 nm non sono economici e i processi a 3 nm, 2 nm e inferiori semplicemente non possono essere implementati.

I clienti utilizzano sempre più spesso il doppio modello EUV per stampare caratteristiche del chip inferiori ai limiti di risoluzione dell’attuale litografia EUV (13 nm) e per ottimizzare l’area e il costo del chip. Questa doppia modellazione richiede un processo di “litho-etch-litho-etch” (LELE) che necessita più tempo e utilizza attrezzature, materiali ed energia aggiuntivi. In questo modo, le dimensioni delle caratteristiche sono state notevolmente ridotte ma a un costo sempre maggiore.

Entrambe le metà del motivo vengono combinate su pellicole intermedie e quindi incise nel wafer. Mentre il doppio patterning è efficace per aumentare la densità delle caratteristiche, aggiunge complessità di design, insieme a fasi di processo che consumano tempo, energia, materiali e acqua, e aumentano il costo dei wafer fabs e della produzione di wafer.

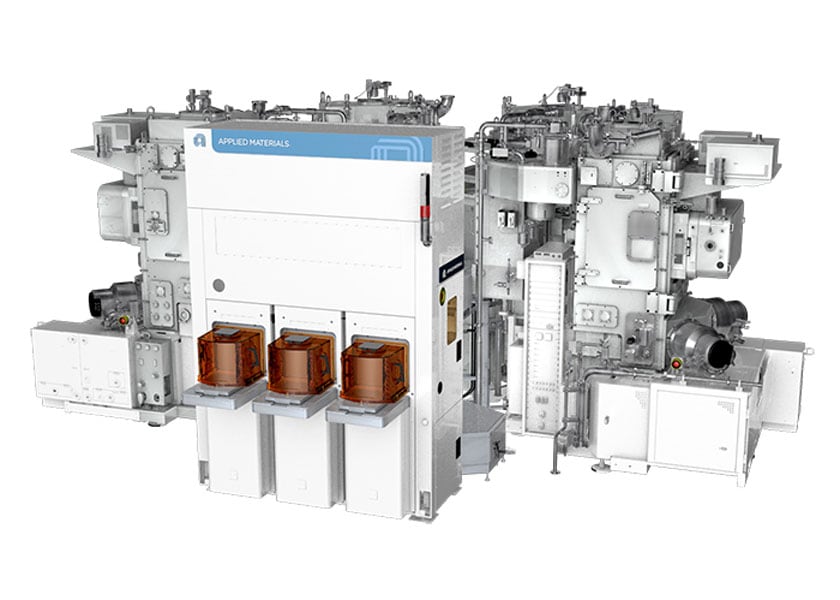

Il sistema di modellazione Centura Sculpta

Per aiutare i produttori di chip a continuare a ridurre i progetti senza i costi aggiuntivi, la complessità e il consumo di energia e materiali del doppio modello EUV, Applied Materials ha lavorato a stretto contatto con i principali clienti per sviluppare il sistema di modellazione Centura Sculpta. I produttori di chip possono ora stampare un singolo modello EUV e quindi utilizzare il sistema Sculpta per allungare le forme in qualsiasi direzione scelta per ridurre lo spazio tra le caratteristiche e aumentare la densità del modello. Poiché il modello finale viene creato da una singola maschera, i costi e la complessità del progetto vengono ridotti e il rischio di resa dovuto agli errori di allineamento del doppio modello viene eliminato.

Il doppio patterning EUV richiede una serie di fasi del processo di produzione aggiuntive che generalmente includono la deposizione di film di patterning CVD, la pulizia CMP, la deposizione e la rimozione di fotoresist, la litografia EUV, la metrologia eBeam, l’incisione del film di patterning e la pulizia dei wafer. Per ogni sequenza di doppio patterning EUV che sostituisce, il sistema Sculpta può fornire ai produttori di chip:

- una riduzione dei costi di capitale di circa 250 milioni di dollari USA per 100.000 avviamenti di wafer al mese di capacità produttiva;

- risparmi sui costi di produzione di circa 50 dollari per wafer;

- Risparmio energetico di oltre 15 kWh per wafer

- Riduzione diretta delle emissioni di gas serra di oltre 0,35 kg di CO2 equivalente per wafer

- Risparmio idrico di circa 15 litri per wafer

“Il nuovo sistema Sculpta è un ottimo esempio di come i progressi nell’ingegneria dei materiali possano integrare la litografia EUV per aiutare i produttori di chip a ottimizzare l’area e il costo dei chip, affrontando al contempo le crescenti sfide economiche e ambientali della produzione di chip avanzati“, ha affermato il dott. Prabu Raja, Vicepresidente senior e General Manager del Semiconductor Products Group presso Applied Materials. “L’esclusiva tecnologia di modellazione del sistema Sculpta combina la profonda esperienza di Applied nelle tecnologie di rimozione dei materiali e del nastro per creare un’innovazione rivoluzionaria per il toolkit dell’ingegnere di modellazione“.

Gli strumenti di litografia EUV ora costano quasi 170 milioni di dollari ciascuno e gli strumenti di prossima generazione ad alta NA (apertura numerica) di ASML potrebbero costare il doppio. High-NA ridurrà il limite di risoluzione a 8 nm, riducendo la necessità di pattern multipli, ma non immediatamente; le prime macchine sono in consegna entro il 2024.

Nel frattempo, la litografia rappresenta circa il 35% del costo di produzione a 3 nm con ASML cha ha attualmente il monopolio sulla litografia EUV.

“Poiché la legge di Moore ci spinge a prestazioni e densità di elaborazione sempre maggiori, il pattern shaping si sta rivelando una nuova tecnologia importante che può aiutare a ridurre i costi di produzione e la complessità dei processi e a conservare energia e risorse“, ha affermato Ryan Russell, vicepresidente per lo sviluppo della tecnologia logica presso Intel Corp. “Avendo collaborato a stretto contatto con Applied Materials nell’ottimizzazione di Sculpta attorno alla nostra architettura di processo, Intel implementerà funzionalità di modellazione dei modelli per ridurre i costi di progettazione e produzione, i tempi del ciclo di processo e l’impatto ambientale.”

“Quando si spingono i limiti del patterning, è necessario considerare tre aspetti critici: spaziatura da punta a punta, difetti del ponte del pattern e rugosità del bordo della linea“, ha affermato Parco Jong Chul, Master of Foundry Etch Technology Team presso Samsung Electronics. “In qualità di partner di sviluppo iniziale dell’innovativa tecnologia di modellazione dei modelli, credo che il sistema Sculpta di Applied sia un’affascinante svolta che affronta queste sfide di modellazione e riduce i costi di produzione per i produttori di chip in tutto il mondo“.

“Il nuovo sistema Sculpta di Applied Materials è una rivoluzione nella modellazione che offre una capacità completamente nuova ai produttori di chip“, ha affermato Dan Hutchson, Vice presidente, TechInsights. “Poiché l’industria continua a spingere i limiti del ridimensionamento dei chip, abbiamo bisogno di scoperte come la tecnologia di modellazione dei modelli di Applied che può migliorare la potenza, le prestazioni, l’area e il costo dei chip, riducendo al contempo i costi di progettazione e il consumo di energia e materiali. Sculpta è la nuova fase di processo più innovativa nella fabbricazione di wafer dall’introduzione del CMP.”

La CMP (planarizzazione chimico-meccanica), che viene utilizzata per rimuovere il materiale in eccesso e creare una superficie liscia del wafer, è una delle numerose fasi del processo di produzione, oltre alla litografia EUV, che sarà interessata dall’introduzione di Sculpta.

Il pattern shaping potrebbe aiutare Intel a raggiungere TSMC e Samsung e quindi accelerare la crescita del mercato della litografia EUV.

Sculpta è un nuovo prodotto ma il pattern shaping non è una nuova tecnologia: Applied Materials ha pubblicato documenti di ricerca sull’argomento da diversi anni e le organizzazioni di ricerche di mercato riferiscono che Intel potrebbe introdurlo a 1,8 nm nel 2024 o 2025. Samsung dovrebbe essere il secondo utente e TSMC il terzo, molto probabilmente a 1,4 nm.

Questa svolta tecnologica rende ancora più lontana la distanza della tecnologia cinese da quella occidentale e dimostra quanto la Cina abbia bisogno di questi progressi per fare avanzare la propria industria dei chip.

Il nuovo sistema metrologico CD-SEM VeritySEM 10

Sempre il 28 febbraio, Applied Materials ha presentato il nuovo sistema metrologico VeritySEM 10.

I produttori di chip utilizzano CD-SEM per effettuare misurazioni sub-nanometriche dei modelli una volta che uno scanner litografico li trasferisce da una maschera a un fotoresist. Queste misurazioni calibrano continuamente le prestazioni del processo di litografia per garantire che i modelli siano corretti prima che vengano incisi nel wafer. I CD-SEM vengono utilizzati anche dopo l’incisione per correlare i modelli previsti con i risultati sul wafer. I CD-SEM aiutano quindi a controllare il processo di incisione e consentono un ciclo di feedback tra litografia e incisione che fornisce agli ingegneri set di dati altamente correlati per la messa a punto olistica del processo.

Misurare le dimensioni critiche delle caratteristiche del dispositivo a semiconduttore diventa più impegnativo man mano che i fotoresist diventano più sottili con EUV e in particolare High-NA EUV. Per acquisire immagini ad alta risoluzione che forniscano misurazioni sub-nanometriche accurate, il CD-SEM deve essere in grado di applicare con precisione uno stretto eBeam alla piccola area occupata dal fotoresist estremamente sottile. L’energia dell’eBeam interagisce con i fotoresist e, se l’energia di atterraggio è troppo elevata, il resist si ridurrà, distorcendo il modello e creando errori. I CD-SEM convenzionali non possono produrre fasci sufficientemente stretti da creare immagini ad alta risoluzione con energie di atterraggio sufficientemente basse da ridurre al minimo le interazioni con il delicato High-NA photoresist.

Il nuovo sistema VeritySEM 10 di Applied Materials presenta un’architettura unica che consente una bassa energia di atterraggio a una risoluzione 2 volte migliore rispetto ai CD-SEM convenzionali. Fornisce inoltre una velocità di scansione superiore del 30% per ridurre ulteriormente l’interazione con il fotoresist e aumentare la produttività. La risoluzione e la velocità di scansione leader del settore del sistema forniscono un migliore controllo dei processi di litografia e incisione EUV e High-NA EUV per aiutare i produttori di chip ad accelerare lo sviluppo del processo e massimizzare la resa nella produzione ad alto volume.

Il sistema VeritySEM 10 viene adottato anche dai produttori di chip per applicazioni di metrologia dimensionale critica nei progetti 3D, inclusi i transistor logici Gate-All-Around (GAA) e le memorie 3D NAND dove gli elettroni retrodiffusi del sistema consentono l’imaging ad alta risoluzione di strutture profonde. Tra le applicazioni per i chip GAA, VeritySEM 10 viene utilizzato per misurare e caratterizzare il processo di epitassia selettiva che è fondamentale per le prestazioni dei transistor. Per le memorie 3D NAND, il sistema fornisce un ampio campo visivo e un’elevata profondità di messa a fuoco per misurare intere strutture di interconnessione a scala e aiutare a mettere a punto le procedure del processo di incisione.

“Il sistema VeritySEM 10 è una svolta nella tecnologia CD-SEM che risolve le sfide metrologiche delle principali inflessioni tecnologiche che daranno forma al settore negli anni a venire“, ha affermato Keith Wells, Group Vice President of Imaging and Process Control presso Applied Materials. “La combinazione unica del sistema di bassa energia di atterraggio, alta risoluzione e velocità di imaging più rapida aiuta a spianare la strada a High-NA EUV, transistor Gate-All-Around e NAND 3D ad alta densità”.

Il sistema VeritySEM 10 sta riscuotendo un forte interesse commerciale da parte dei principali clienti di logica e memoria, con oltre 30 sistemi spediti nell’ultimo anno. Diversi clienti hanno selezionato il sistema come strumento di sviluppo per i transistor GAA. Tutti i principali clienti 3D NAND hanno scelto il sistema come strumento di registrazione per lo sviluppo e il processo e diversi clienti DRAM lo hanno scelto come strumento di registrazione per il processo.