La nuova tecnologia messa a punto da Toshiba per i propri MOSFET al carburo di silicio (SiC) consente una significativa riduzione della resistenza in conduzione e delle perdite di commutazione quantificabili in circa il 20% rispetto ai MOSFET di seconda generazione dell’azienda.

I dispositivi di alimentazione sono componenti essenziali per la gestione e la riduzione del consumo di energia in tutti i tipi di apparecchiature elettroniche e per realizzare una società carbon neutral. Il SiC è ampiamente considerato come il materiale di prossima generazione per i dispositivi di potenza, poiché fornisce tensioni più elevate e perdite inferiori rispetto al silicio. Mentre i dispositivi di potenza SiC sono ora utilizzati principalmente negli inverter per i treni e nell’elettrificazione dei veicoli, applicazioni più ampie sono all’orizzonte, in particolare in ambito industriale. Negli anni, l’adozione e la crescita del mercato dei dispositivi SiC sono state frenate da problemi di affidabilità.

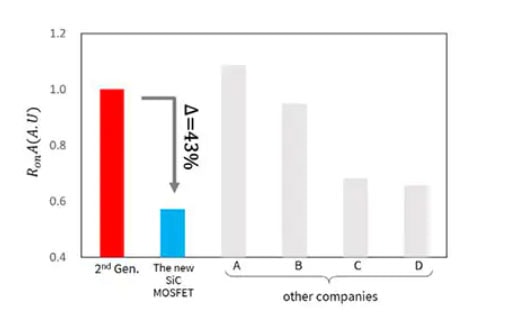

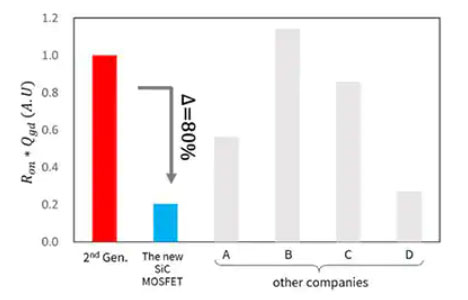

Toshiba ha risolto questi problemi adottando una struttura in cui un diodo Schottky Barrier Diode (SBD) è posto in parallelo al diodo PN all’interno del MOSFET SiC di seconda generazione dell’azienda. Tuttavia, questa architettura ha creato un nuovo problema, con le prestazioni del MOSFET che si deteriorano quando il dispositivo non funziona come MOSFET. Nello specifico si registra un aumento della resistenza ON per unità di superficie (RonA) e dell’indice di prestazione che indica la resistenza ON e l’alta velocità (Ron*Qgd). Un ulteriore problema è rappresentato dal costo unitario più elevato derivante dall’aumento dell’area del chip per ridurre la resistenza in conduzione (Ron).

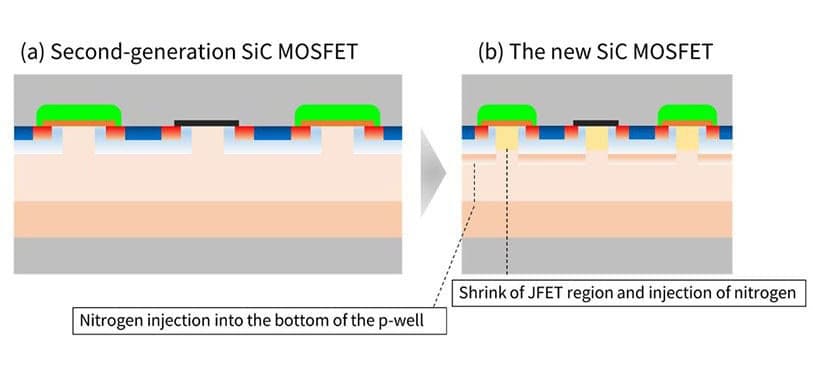

Toshiba ha ora sviluppato un’architettura che riduce RonA includendo un SBD. Il valore della resistenza di diffusione (Rspread) viene ridotta e la corrente SBD viene aumentata iniettando azoto nella parte inferiore dell’ampia regione di diffusione di tipo p (p-well) del MOSFET SiC.

Toshiba ha anche ridotto la regione JFET e ha iniettato azoto per ridurre la capacità di feedback e la resistenza JFET. Di conseguenza, la capacità di feedback è stata ridotta senza aumentare RonA. Toshiba ha verificato che questa struttura del dispositivo riduce RoinA del 43%, Ron*Qgd dell’80%, e perdita di commutazione (da accensione a spegnimento) di circa il 20% rispetto ai suoi prodotti di seconda generazione. Il funzionamento stabile senza fluttuazione di RonA è stato garantito anche dal posizionamento ottimizzato dell’SBD.

I dettagli di questa tecnologia sono stati presentati da Toshiba durante PCIM Europe 2022. Toshiba prevede di avviare la produzione in serie di MOSFET SiC di terza generazione con la nuova tecnologia alla fine di agosto di quest’anno.